ISSN (Online): 2320-9364, ISSN (Print): 2320-9356

www.ijres.org Volume 10 Issue 12 | December 2022 | PP. 72-78

# **Lossy Grounded Inductor Simulators with Electronic Tunability**

<sup>1</sup>Devesh Tripathi, <sup>1</sup>Shri Om Mishra, <sup>1</sup>Ramapati Mishra, <sup>1</sup>Ashutosh Kumar Singh

<sup>1</sup>Department of Electronicsand Communication Engineering, Institute of Engineering and Technology, Dr. Ram Manohar LohiaAvadh University, Ayodhya, India Corresponding Author:devesh9411@gmail.com

#### Abstract

In this paper two new designs of lossy grounded inductor simulators (GIS) are proposed. The designs employ a highly versatile active element the dual X current conveyor differential input transconductance amplifier (DXCCDITA). The inductor simulators require three passive components, two grounded resistors and one capacitor. The realised inductance can be tuned electronically. There is no need of passive component matching for realizing the inductance. The non-ideal analysis is carried out to study the effect of process and component spread on the performance of the designed GIS. The simulations are conducted using 0.35  $\mu$ m CMOS technology at a supply voltage of  $\pm 1.5$  V. LTspice software is used for the analysis.

**Keywords:** Analog circuits, Current mode, Current conveyor, Signal processing

Date of Submission: 01-12-2022 Date of acceptance: 10-12-2022

## I. INTRODUCTION

Inductors and capacitors are indispensable components in analog circuits [1]. The major limitations curtailing the use of the synthetic inductors are their bulky nature, high cost, requirement of large silicon area and lack of electronic tunability [1-2]. The floating capacitors with large values are also difficult to design and fabricate. Moreover, the current fabrication technology supports monolithic inductors of around 1nH and limited quality factors [1-2]. This led to the research in the active simulation of inductors and capacitors. The generalized active immittance simulators finds applications in LC oscillators, for parasitic cancellation, impedance matching, active filters, phase shifters and resonators etc. [1-6]. The immittance simulation can be divided into two categories grounded immittance and floating immittance simulation. The actively simulated immittance include inductors, capacitor multipliers and frequency dependent negative resistors.

The inductor simulation finds multitude of applications especially in higher order filter design. A popular method of higher order filter synthesis is LRC ladder filter simulation. It also a well-established fact that a ladder filter has minimum components sensitivity. The major limitation that arises in ladder filter simulation is the requirement of high valued one or more grounded or floating inductors which render it incompatible with today's low voltage and miniature size systems. In order to judiciously use each micron of chip area researchers utilize inductor simulation techniques in which an active element along with RC components emulate the behavior of a passive inductor. This approach provides many advantages to elaborate a few (i) the chip area required is reduced (ii) large value inductors with acceptable quality factors can be synthesized (iii) by employing modern active blocks like current conveyors on chip tunable inductors can be developed (iv) floating inductors can also be easily realized. Another important simulation is that of capacitor multiplier. In some filter applications large, valued capacitors are required which are difficult to fabricate owing to large chip area. Moreover, present day's deep submicron technology does not support large valued integrated capacitors. To overcome this scenario, active simulation of capacitors where active device along with small values RC network emulated the behavior of a large passive capacitor. A small value capacitor along with resistors and active blocks give large value active capacitors, hence the capacitor multipliers.

The inductor simulators can be categorized based on number of active blocks used, number of passive elements employed and whether they emulate lossy or loss less inductance. The simulators presented in [1, 11-13, 15, 16, 17, 21-23] use single active block but require passive components more than three and also passive components matching to realize inductance. The designs proposed in [5, 10, 12, 14-17, 19, 21-24] use one or more floating capacitors and/or resistors for implementing inductance. Although floating capacitor can be easily fabricated in the modern technology. The use of floating capacitor is not desirable for integrated circuit implementation as it requires die area and effects noise performance. The designs proposed by [4, 12, 13, 23] employ two or more active blocks and excessive passive elements resulting in more chip area and parasitic effects. The designs proposed in [1, 4, 5, 11-24, 29, 30] did not provide inbuilt tunability of the inductance. The

www.ijres.org 72 | Page

designs in [10, 28] have inbuilt tunability to tune the simulated inductance which is very advantageous. A detailed comparison of the exemplary inductance topologies available in the literature is done. The literature survey reveals that the drawbacks of the majority of the presented inductor simulators are (i) no provision for on chip tunability (ii) use of more than one active element (iii) use of floating capacitor (iv) excessive use of passive elements (v) passive components matching requirement.

#### II. Dual X Current Conveyor Differential Input Transconductance Amplifier (DXCCDITA)

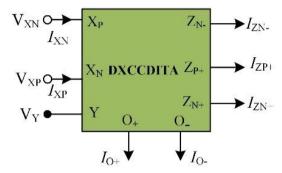

The Dual X current conveyor differential input transconductance amplifier (DXCCDITA) [31] is a very flexible active element that has features of current conveyor (CCII), inverting current conveyor (ICCII) and operational transconductance amplifier (OTA) in a single integrated package. The OTA provides inbuilt tunability to the active element. The block of DXCCDITA is given in Fig.1 and the current-voltage relations are presented in Equations (1-6).

Figure 1. Block Diagram of DXCCDITA

$$I_{XP} = I_{ZP+} = -I_{ZP-} (1)$$

$$I_{XN} = I_{ZN+} = -I_{ZN-} (2)$$

$$V_V = V_{XP} = -V_{XN} \tag{3}$$

$$I_{0+} = -I_{0-} = g_m(V_{ZP+} - V_{ZN+})$$

(4)

The expression for transconductance  $(g_m)$  is given in Equation 5.

$$g_m = \sqrt{\mu_n C_{OX} \left(\frac{W}{L}\right)_{25,26} I_{Bias}}$$

(5)

where  $C_{OX}$  is the gate oxide capacitance,  $\mu_n$  is the mobility of electrons in NMOS,  $g_m$  denotes the transconductance of OTA set via bias current  $I_B$  and  $\frac{W}{L}$  is the aspect ratio of the transistors.

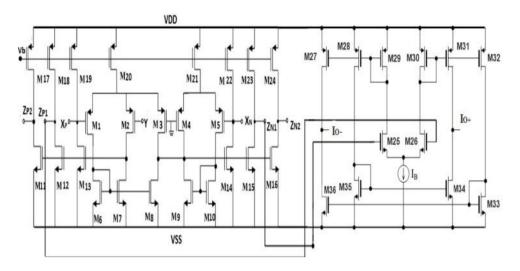

The CMOS implementation of the DXCCDITA is presented in Fig. 2. The f is low impedance current input node. The  $X_+$ ,  $X_-$ , Z &  $Z_C$  terminals are high impedance current output nodes. The number of current output terminals ( $I_{ZC}$ ,  $X_+$ ,  $X_-$ ) can be increased by simply adding two MOS transistors.

www.ijres.org 73 | Page

Figure 2: CMOS implementation of DXCCDITA

### III. Non-Ideal Analysis of DXCCDITA

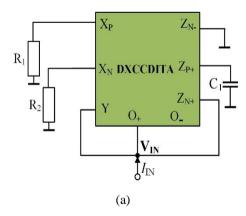

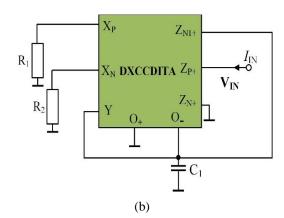

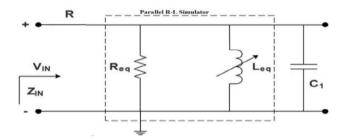

The proposed inductor simulators using a single DXCCDITA, and grounded passive elements are shown in Fig.3. The analysis of the circuits leads to the inductance values as presented in Equations (6-7). The proposed inductors have inbuilt tunability and requires minimum number of passive components. Additionally, there is passive components matching for realizing the inductance.

Inspection of Equations (6-7) reveals that the GIS-1 and GIS-2 implements lossy parallel and series inductors respectively. It is noteworthy that the value of the parallel resistor in GIS-1 can be set using resistor  $R_1$  independent of the inductance value that is set by  $R_2$  and  $g_m$  which is an advantage. The series resistance in GIS-2 can be altered by changing  $R_1$  without affecting the inductance that can be set via  $R_2$ .

$$\frac{1}{L_{eq}} + \frac{1}{R_{eq}} = \frac{V_{IN}}{I_{IN}} = \frac{g_{m}}{SC_{1}R_{2}} + \frac{1}{R_{1}}$$

(6)

$$L_{eq} + R_{eq} = \frac{V_{IN}}{I_{IN}} = \frac{SC_1R_2}{g_m} + \frac{R_2}{R_1g_m}$$

(7)

www.ijres.org 74 | Page

Figure3: Proposed Inductor Simulators(a) GIS-1(b) GIS-2

#### IV. RESULT AND DISCUSSION

To test the proposed inductor simulators the DXCCDITA is designed in CMOS 0.13 $\mu$ m TSMC technology. The simulations are carried out in LTspice software for validating the designs. The DXCCDITA is simulated at a supply voltage of  $\pm 1.5$ V. The bias current of the OTA was fixed at  $50\mu$ A to set the transconductance ( $g_m$ )=0.1mS.

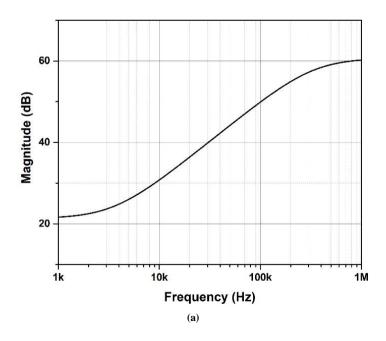

The lossy parallel inductor GIS-1 is analysed. It is designed for L=1.25mS in parallel with R=5k $\Omega$ . The passive component values are set as  $R_1=R_2=5k\Omega$ ,  $C_1=50pF$  and  $g_m$ =0.1mS. The parallel resistance value can be independently set by  $R_1$  without affecting the realised inductance. The AC analysis results presented in Fig. 4 confirms the working.

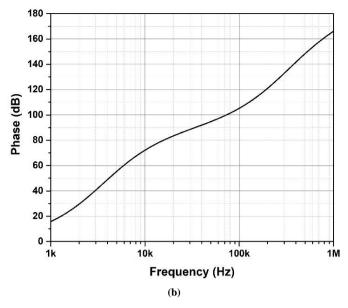

The lossy series RC inductor simulator GIS-2 is also tested. It is designed for L=1.25mS in series with R=10k $\Omega$ . The passive component values are selected as  $R_1=R_2=5k\Omega$ ,  $C_1=50pF$ . The AC results presented in Fig. 5 confirms the correct functioning of the simulator.

www.ijres.org 75 | Page

Figure 4: The GIS-1 (a) gain and (b) phase response

Figure5: The GIS-2 (a) gain and (b)phase response

www.ijres.org 76 | Page

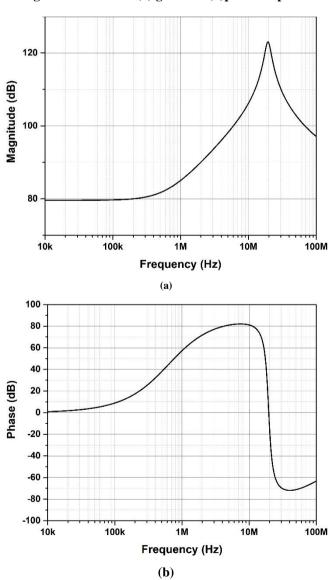

The lossy parallel RL inductor simulator is put to use for designing and RLC resonance circuit presented in Fig.6. The passive parallel R and L in the circuit are replaced by active RL simulator GIS-1. The RLC circuit if designed for a resonance frequency of 0.5MHz by setting  $R_{eq}=10k\Omega$ ,  $L_{eq}=1mH$  and  $C_1=100pF$  using the formula for frequency given in Equation 8.

$$\omega_o = \frac{1}{\sqrt{L_{eq} C_1}} \tag{8}$$

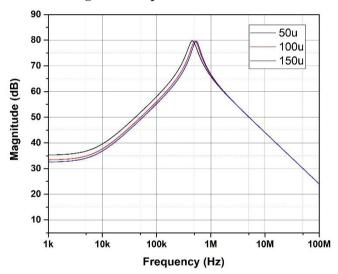

The AC analysis results are plotted for different OTA bias current confirms the working of the filter using GIS-1 Fig. 7 and tunability of filter frequency via OTA bias current.

Figure6: The parallel RLC circuit

Figure7:Frequency response of RLC filter

### V. CONCLUSION

This paper presents two new designs of grounded lossy inductor simulators employing DXCCDITA. The proposed inductor simulators require only grounded passive components for realization and have electronic tuning capability. The proposed simulators are examined using mathematical analysis and the effect of non-ideal current and voltage gains on their performance is also examined. The inductor simulators are validated by using them to design many passive filter circuits. The LTspice software is used for the design and verification. The simulation results are found consistent with the theoretical predictions.

#### REFERENCES

- [1]. Ibrahim, M. A., Minaei, S., Yuce, E., Herencsar, N., &Koton, J. (2012). Lossy/Lossless Floating/Grounded Inductance Simulation Using One DDCC. Radioengineering, 21(1).

- [2]. Floating inductance, FDNR and capacitance simulation circuit employing only grounded passive elements. International Journal of Electronics, 93(10), 679-688.

- [3]. Metin, B., &Cicekoglu, O. (2006). A novel flating lossy inductance realization topology with NICs using current conveyors. IEEE Transactions On Circuits And Systems II: Express Briefs, 53(6), 483-486.

- [4]. Cicekoglu, M. O. (1998). Active simulation of grounded inductors with CCII+ s and grounded passive elements. International Journal of Electronics, 85(4), 455-462.

- [5]. Alpaslan, H., &Yuce, E. (2015). Inverting CFOA based lossless and lossy grounded inductor simulators. Circuits, Systems, and Signal Processing, 34(10), 3081-3100.

- [6]. Ferri, G., & Guerrini, N. C. (2003). Low-voltage lowpower CMOS current conveyors. Springer Science & Business Media.

www.ijres.org 77 | Page

- [7]. Mohan, P. A. (2012). Current-mode VLSI analog fiters: design and applications. Springer Science & Business Media.

- [8]. Alzaher, H. A. (2008). A CMOS digitally programmable universal current-mode fiter. IEEE Transactions on Circuits and Systems II: Express Briefs, 55(8), 758-762.

- [9]. Van Valkenburg, M. E. (1982). Analog fiter design (pp. 136-137). Holt, Rinehart, and Winston.

- [10]. Pathak, J. K., Singh, A. K., &Senani, R. (2016). New canonic lossy inductor using a single CDBA and its application. International Journal of Electronics, 103(1), 1-13.

- [11]. Metin, B. (2012). Canonical inductor simulators with grounded capacitors using DCCII. International Journal of Electronics, 99(7), 1027-1035.

- [12]. Pandey, R., Pandey, N., Paul, S. K., Singh, A., Sriram, B., & Trivedi, K. (2011). New topologies of lossless grounded inductor using OTRA. Journal of Electrical and Computer Engineering, 2011, 7.

- [13]. Yuce, E., &Minaei, S. (2017). Commercially Available Active Device Based Grounded Inductor Simulator and Universal Filter with Improved Low Frequency Performances. Journal of Circuits, Systems and Computers, 26(04), 1750052.

- [14]. Metin, B., Herencsar, N., Koton, J., &Horng, J. W. (2014). DCCII-based novel lossless grounded inductance simulators with no element matching constrains. Radioeng J, 23, 532-4538.

- [15]. Çam, U., Kaçar, F., Cicekoglu, O., Kuntman, H., &Kuntman, A. (2003). Novel grounded parallel immittance simulator topologies employing single OTRA. AEU-International Journal of Electronics and Communications, 57(4), 287-290.

- [16]. Yuce, E., Minaei, S., &Cicekoglu, O. (2005). A novel grounded inductor realization using a minimum number of active and passive components. Etri Journal, 27(4), 427-432.

- [17]. Yuce, E., Minaei, S., &Cicekoglu, O. (2006). Limitations of the simulated inductors based on a single current conveyor. IEEE Transactions on Circuits and Systems I: Regular Papers, 53(12), 2860-2867.

- [18]. Yuce, E., &Minaei, S. (2008). A modifid CFOA and its applications to simulated inductors, capacitance multipliers, and analog fiters. IEEE Transactions on Circuits and Systems I: Regular Papers, 55(1), 266-275.

- [19]. Yuce, E. (2009). Novel lossless and lossy grounded inductor simulators consisting of a canonical number of components. Analog Integrated Circuits and Signal Processing, 59(1), 77-82.

- [20]. Yuce, E., &Minaei, S. (2009). On the realization of simulated inductors with reduced parasitic impedance effcts. Circuits, Systems, and Signal Processing, 28(3), 451-465.

- [21]. Kumar, P., &Senani, R. (2010). New grounded simulated inductance circuit using a single PFTFN. Analog Integrated Circuits and Signal Processing, 62(1), 105.

- [22]. Kaçar, F., &Yeşil, A. (2010). Novel grounded parallel inductance simulators realization using a minimum number of active and passive components. Microelectronics Journal, 41 (10), 632-638.

- [23]. Gupta, A., Senani, R., Bhaskar, D. R., & Singh, A. K. (2012). OTRA-based grounded-FDNR and grounded-inductance simulators and their applications. Circuits, Systems, and Signal Processing, 31 (2), 489-499.

- [24]. Kacar, F., & Kuntman, H. (2011). CFOA-based lossless and lossy inductance simulators. Radioengineering, 20(3), 627-631.

- [25]. Kaçar, F., Yeşil, A., Minaei, S., &Kuntman, H. (2014).

- [26]. Positive/negative lossy/lossless grounded inductance simulators employing single VDCC and only two passive elements. AEU-International Journal of Electronics and Communications, 68(1), 73-78.

- [27]. M. Faseehuddin, J. Sampe, S. Shireen, and S. H. M. Ali, "Lossy and lossless inductance simulators and universal filters employing a new versatile active block," Informacije MIDEM, vol. 48, pp. 97-114, 2018.

- [28]. Yuce, E., Safari, L., Minaei, S., Ferri, G., Barile, G. and Stornelli, V., 2021. A new simulated inductor with reduced series resistor using a single VCII±. Electronics, 10(14), p.1693.

- [29]. Bhaskar, D.R. and Kumar, P., 2022. Single operational transresistance amplifier based grounded resistance controlled synthetic inductor configuration. International Journal of Circuit Theory and Applications.

- [30]. Nagar, B.C. and Paul, S.K., 2021. Lossless grounded admittance simulator using OTRA. Analog integrated circuits and signal processing, 106(3), pp.649-659.

- [31]. Mohammad, F., Sampe, J., Shireen, S. and Ali, S.H.M., 2017. Minimum passive components based lossy and lossless inductor simulators employing a new active block. AEU-International Journal of Electronics and Communications, 82, pp.226-240.

www.ijres.org 78 | Page